تطوير الصناعة

تحسين كبير في خصائص الترانزستور الجرمانيوم متعدد البلورات

قام أحد التعاونيين البحثيين بتطوير تقنية جديدة لتشكيل الأفلام متعددة البلورات لتحقيق تقنية التراص ثلاثية الأبعاد (3D) للدوائر المتكاملة واسعة النطاق (LSIs)، مما أدى إلى تحسين أداء ترانزستورات الجرمانيوم متعدد البلورات من النوع N (Ge) بشكل كبير.

يمكن تشكيل Ge متعدد البلورات عند درجة حرارة أقل (500 درجة مئوية أو أقل) من السيليكون متعدد البلورات (Si) المستخدم على نطاق واسع. وهذا يسمح بتكديس دوائر CMOS مباشرة دوائر متكاملة دون التسبب في ضرر حراري، وهو أمر واعد كتقنية أساسية لـ 3D-LSI. بالإضافة إلى ذلك، فإن حركة الإلكترونات والثقوب في Ge أعلى منها في Si، لذلك من المتوقع تشغيل عالي السرعة وتشغيل منخفض الجهد. الترانزستورات من النوع N والنوع P مطلوبة لعمليات الدوائر المتكاملة. لقد حققت الترانزستورات من النوع P من Ge متعدد البلورات بالفعل أداءً كافيًا يقترب من أداء ترانزستورات Si التقليدية أحادية البلورة. ومع ذلك، فإن تيار القيادة للترانزستورات من النوع N أقل من تيار ترانزستورات Si التقليدية بمقدار 10 مرات أو أكثر، وهو ما كان يمثل مشكلة. أدت التكنولوجيا المتقدمة إلى زيادة تيار القيادة بحوالي 10 أضعاف مقارنة بالتكنولوجيا التقليدية، لذلك من المتوقع أن تكون سرعة تشغيل دوائر Ge المتكاملة متعددة البلورات عند المستوى المطلوب للاستخدام العملي والمساهمة في تحقيق أجهزة 3D-LSI.

تم الإعلان عن تفاصيل التكنولوجيا المطورة في "الاجتماع الدولي للأجهزة الإلكترونية 2014" الذي سيعقد في سان فرانسيسكو بالولايات المتحدة الأمريكية في الفترة من 15 إلى 17 ديسمبر 2014.

في هذه الأيام، يمتلك العديد من الأشخاص أجهزة تكنولوجيا المعلومات مثل الهواتف الذكية والأجهزة اللوحية، وقد زادت كمية المعلومات المعالجة بشكل كبير. في حين أن هناك حاجة إلى مزيد من التحسين في قدرة معالجة المعلومات لأجهزة تكنولوجيا المعلومات، فإن كمية الطاقة التي تستهلكها آخذة في الازدياد، لذا فإن توفير استهلاك طاقة منخفض للغاية لأجهزة تكنولوجيا المعلومات هذه يعد أمرًا مهمًا في تعزيز مجتمع يستهلك طاقة أقل. في حين تم تحقيق الأداء العالي والاستهلاك المنخفض للطاقة من LSIs من خلال تصغير الترانزستورات حتى الآن، فقد أثبت المزيد من التصغير أنه يمثل تحديًا تقنيًا واقتصاديًا. وفي الوقت نفسه، لا توفر الدوائر المتكاملة ثلاثية الأبعاد التي تم فيها تكديس العديد من LSIs تكاملًا عاليًا وأداءً عاليًا دون الحاجة إلى تقنية التصغير فحسب، بل توفر أيضًا فوائد توفير الطاقة عن طريق تقليل تأخير الأسلاك. لقد تم تطوير وسيلة لإنشاء أغشية رقيقة من LSIs التي تم إنشاؤها بشكل فردي وتكديسها ولكنها مكلفة ولا تعمل على تحسين كثافة الأسلاك بشكل كافٍ. ولذلك فمن المرغوب فيه أن يكون لديك تقنية 3D-LSI جديدة تعمل على تشكيل دوائر CMOS بحيث يتم تكديسها بشكل مستمر في طبقة الأسلاك من دوائر CMOS المتكاملة وتوصيلها بالأسلاك العلوية والسفلية.

بالتعاون مع تسوتومو تيزوكا (أخصائي أبحاث مركزة محددة)، وكوجي أوسودا (أخصائي أبحاث مركزة محددة) (كلاهما يعمل حاليًا في شركة Toshiba)، وآخرين من مجموعة تطوير المواد الجديدة/الهيكل الجديد CMOS، فريق البحث التعاوني Green Nanoelectronics Center (GNC) التي تم إنشاؤها في معهد أبحاث الإلكترونيات النانوية التابع لـ AIST، بحلول نهاية مارس 2014، أجرت بحثًا تعاونيًا يتعلق بـ P-type وN-type MOSFET باستخدام Polycrystalline Ge (بيان صحفي لـ AIST بتاريخ 12 ديسمبر 2013). يهدف هذا البحث إلى تطوير LSIs ذات أداء أعلى وتستهلك طاقة أقل. من خلال البحث الحالي، تم تقديم عمليات إنتاج جديدة، مما أدى إلى تطوير ترانزستورات Ge متعددة البلورات من النوع N بأداء أعلى.

تم إجراء هذا البحث (من السنة المالية 2010 إلى السنة المالية 2013) في GNC بمساعدة برنامج تمويل البحث والتطوير المبتكر الرائد عالميًا في مجال العلوم والتكنولوجيا التابع للجمعية اليابانية لتعزيز العلوم، وهو نظام صممه مجلس سياسات العلوم والتكنولوجيا.

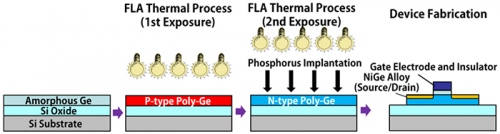

يتم تشكيل فيلم Ge متعدد البلورات الذي يشكل الترانزستورات على النحو التالي: يتم تشكيل طبقة أكسيد حراري (SiO2) على ركيزة Si، ثم يتم استخدام طريقة الرش لترسيب فيلم Ge غير متبلور والذي يتم بعد ذلك بلورته عن طريق المعالجة الحرارية باستخدام التلدين بمصباح الفلاش ( فلا). عندما يتم استخدام طبقة Ge متعددة البلورات هذه لتشكيل ترانزستور، فإن درجة الحرارة المستخدمة في العمليات التي تتبع المعالجة الحرارية تبلغ 350 درجة مئوية كحد أقصى، دون التسبب في أي ضرر، حتى في حالة وجود دائرة متكاملة تتضمن أسلاك نحاسية على الركيزة. يحتوي النموذج الأولي للترانزستور على بنية ترانزستور بدون وصلات مع شكل الزعنفة الموضح في المخططات في الملخص (المخطط المفاهيمي والرسم التخطيطي للهيكل). يجب أن تكون أجزاء القناة والمصدر/المصرف في ترانزستور من النوع N بدون وصلات من النوع N. ومع ذلك، نظرًا لأن Ge متعدد البلورات يكون عادةً من النوع P، كان من الضروري تحويل طبقة Ge متعدد البلورات إلى النوع N، مع الحفاظ على الجودة. للقيام بذلك، بعد المعالجة الحرارية الأولى بطريقة FLA، تم زرع شوائب من النوع N (الفوسفور)، وتم إجراء FLA مرة ثانية لتنشيط هذه الشوائب (الشكل 1). تمكنت طريقة FLA المكونة من خطوتين من إنتاج فيلم Ge متعدد البلورات عالي الجودة من النوع N.

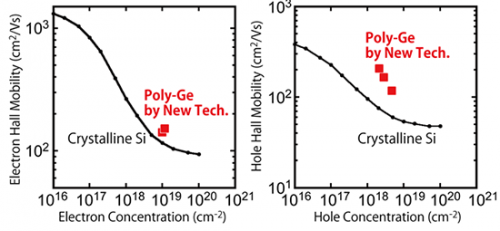

يوضح الشكل 2. حركة تأثير Hall التي تمثل جودة فيلم Ge متعدد البلورات الذي يتم إنتاجه بهذه الطريقة. كان لكل من أفلام Ge متعددة البلورات من النوع N (الإلكترونات) والنوع P (الثقوب) قدرة على الحركة تفوق قدرة التنقل أحادية البلورة سي. يوضح هذا أنه يمكن إنشاء ترانزستور ذو خصائص متفوقة على Si أحادي البلورة باستخدام فيلم Ge متعدد البلورات الذي تم تشكيله بالطريقة المطورة.

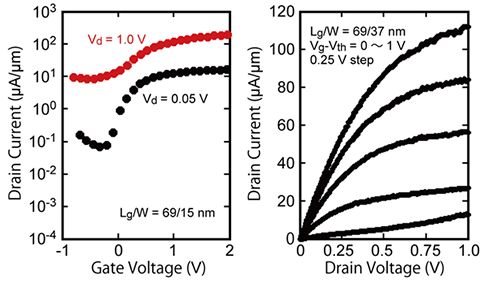

تم إنتاج ترانزستور Ge متعدد البلورات من النوع N بدون وصلات (طول البوابة: 70 نانومتر) من خلال معالجة فيلم Ge متعدد البلورات من النوع N الموصوف أعلاه في شكل زعنفة بالإضافة إلى تشكيل سبيكة النيكل وإبرة الراعي (سبائك Ni-Ge) في مناطق المصدر والصرف. تظهر خصائص النقل والإخراج في الشكل 3. تقترب قيمة تيار التصريف عند جهد تشغيل قدره 1 فولت من 120 ميكرو أمبير/ ميكرومتر تقريبًا، وهي قيمة أكبر بحوالي 10 مرات من القيمة التقليدية وتعادل MOSFET متعدد البلورات من النوع Si N من نفس الحجم تقريبا. ويعتقد أن طريقة FLA المكونة من خطوتين حسنت معدل تنشيط الشوائب مقارنة بالقيمة التقليدية، مما أدى إلى تقليل المقاومة الطفيلية. أدت التكنولوجيا المتقدمة إلى تحسين سرعة تشغيل الترانزستور من النوع N بشكل ملحوظ، والذي كان يُنظر إليه سابقًا على أنه "عنق الزجاجة" في تشغيل الدوائر المتكاملة لترانزستورات Ge متعددة البلورات. تتمتع ترانزستورات Si متعددة البلورات، والتي تميل إلى مقارنتها بترانزستورات Ge متعددة البلورات، بأداء أقل عمومًا من ترانزستورات Si أحادية البلورة. أداء ترانزستورات Ge متعددة البلورات من النوع P يفوق بالفعل أداء ترانزستورات Si متعددة البلورات وهو على قدم المساواة مع أداء ترانزستورات Si أحادية البلورة. وهكذا حققت الطريقة المطورة تقدمًا كبيرًا نحو تحقيق دارات Ge CMOS متعددة البلورات عالية الأداء.

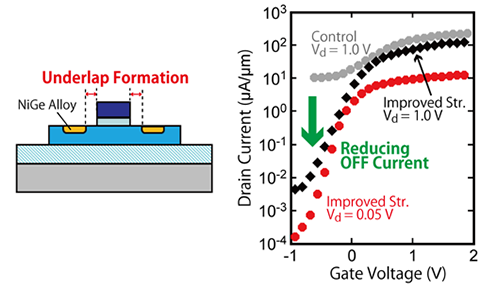

في خصائص النقل في الشكل 3، يكون التيار خارج الحالة كبيرًا، وبالتالي فإن نسبة التشغيل/الإيقاف عند تطبيق 1 فولت كانت حوالي 10 فقط، وهو ما كان يمثل مشكلة. لذلك، من أجل تقليل التيار خارج الحالة، تم تقديم هيكل يوفر مسافات بين أقطاب Ni-Ge والبوابة، مما يقلل التيار خارج الحالة إلى 1/1000 (الشكل 4). في حين انخفض التيار الموجود على الحالة بشكل طفيف، يمكن توقع تيار مرتفع على مستوى الدولة وتيار منخفض خارج الحالة من خلال تحسين المسافات بين أقطاب Ni-Ge والبوابة.

تتضمن الخطط المستقبلية تشكيل دائرة متكاملة تجمع بين Ge متعدد البلورات من النوع P والنوع N الترانزستورات على فيلم عازل والتحقق من تشغيل الدائرة. تتضمن الأهداف الأخرى تطوير 3D-LSI مع Ge متعدد البلورات المكدسة من أجل تصغير LSI بشكل كبير، وزيادة الأداء، وتقليل استهلاك الطاقة.