DÉVELOPPEMENT DE L'INDUSTRIE

Améliore considérablement les propriétés des transistors en germanium polycristallin

Une collaboration de recherche a développé une nouvelle technologie de formation de film polycristallin pour obtenir une technologie d'empilement tridimensionnel (3D) pour les circuits intégrés (LSI) à grande échelle, améliorant considérablement les performances des transistors en germanium (Ge) polycristallins de type N.

Le Ge polycristallin peut être formé à une température plus basse (500 °C ou moins) que le silicium polycristallin (Si) largement utilisé. Cela permet aux circuits CMOS d'être directement empilés sur circuits intégrés sans causer de dommages thermiques, ce qui est prometteur en tant que technologie élémentaire pour le 3D-LSI. De plus, la mobilité des électrons et des trous dans Ge est plus élevée que dans Si, un fonctionnement à grande vitesse et un fonctionnement à basse tension sont donc attendus. Des transistors de type N et de type P sont nécessaires pour les opérations de circuits intégrés. Les transistors de type P en Ge polycristallin ont déjà atteint des performances suffisantes, proches de celles des transistors classiques en Si monocristallin. Cependant, le courant de commande des transistors de type N est 10 fois ou plus inférieur à celui des transistors Si conventionnels, ce qui posait problème. La technologie développée a multiplié par environ 10 le courant de commande par rapport à la technologie conventionnelle, de sorte que la vitesse de fonctionnement des circuits intégrés en Ge polycristallin devrait être au niveau requis pour une utilisation pratique et contribuer à la réalisation de dispositifs 3D-LSI.

Les détails de la technologie développée ont été annoncés lors du « 2014 International Electron Device Meeting » qui se tiendra à San Francisco, aux États-Unis, du 15 au 17 décembre 2014.

De nos jours, de nombreuses personnes possèdent des appareils informatiques tels que des smartphones et des tablettes, et la quantité d’informations traitées a considérablement augmenté. Bien qu'une amélioration supplémentaire de la capacité de traitement de l'information des appareils informatiques soit souhaitée, la quantité d'énergie qu'ils consomment augmente. Il est donc important de fournir à ces appareils informatiques une consommation d'énergie ultra-faible pour promouvoir une société qui consomme moins d'énergie. Même si les performances élevées et la faible consommation d'énergie des LSI ont jusqu'à présent été obtenues grâce à la miniaturisation des transistors, une miniaturisation plus poussée s'est avérée un défi technologique et économique. Parallèlement, les circuits intégrés 3D dans lesquels plusieurs LSI ont été empilés offrent non seulement une intégration élevée et des performances élevées sans nécessiter de technologie de miniaturisation, mais également des avantages en matière d'économie d'énergie en réduisant le retard des câbles. Un moyen de créer des films minces de LSI créés individuellement et de les empiler a été développé, mais il est coûteux et n'améliore pas suffisamment la densité de câblage. Il est donc souhaitable de disposer d'une nouvelle technologie 3D-LSI qui forme des circuits CMOS de manière à les empiler en continu dans une couche de câblage de circuits intégrés CMOS et à les connecter aux fils supérieur et inférieur.

En collaboration avec Tsutomu Tezuka (spécialiste de la recherche concentrée spécifiée), Koji Usuda (spécialiste de la recherche concentrée spécifiée) (tous deux actuellement chez Toshiba Corporation) et d'autres membres du groupe de développement CMOS de nouveaux matériaux/nouvelles structures, l'équipe de recherche collaborative Green Nanoelectronics Center (GNC) établi au sein de l'Institut de recherche en nanoélectronique de l'AIST avait, fin mars 2014, mené des recherches collaboratives sur les MOSFET de type P et de type N utilisant du Ge polycristallin (communiqué de presse de l'AIST du 12 décembre 2013). Cette recherche visait à développer des LSI plus performants et consommant moins d’énergie. Grâce aux recherches actuelles, de nouveaux procédés de production ont été introduits, conduisant au développement de transistors Ge polycristallins de type N offrant des performances encore plus élevées.

Cette recherche a été menée (de 2010 à 2013) au GNC avec l'aide du programme de financement pour une R&D innovante de pointe en science et technologie de la Société japonaise pour la promotion de la science, un système conçu par le Conseil pour la politique scientifique et technologique.

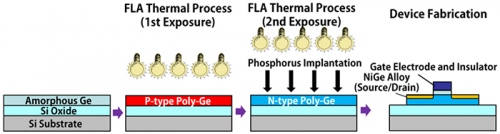

Un film de Ge polycristallin formant des transistors est formé de la manière suivante : une couche d'oxyde thermique (SiO2) est formée sur un substrat de Si, puis la méthode de projection est utilisée pour déposer un film de Ge amorphe qui est ensuite cristallisé par traitement thermique utilisant un recuit par lampe flash ( FLORIDE). Lorsque ce film de Ge polycristallin est utilisé pour former un transistor, la température utilisée dans les processus suivant le traitement thermique est au maximum de 350 °C, sans provoquer de dommages, même si un circuit intégré comprenant des fils de cuivre existe sur le substrat. Le transistor prototype a une structure de transistor sans jonction avec la forme d'aileron illustrée dans les diagrammes du résumé (schéma conceptuel et diagramme schématique de la structure). Les parties canal et source/drain d'un transistor de type N sans jonction doivent toutes être de type N. Cependant, comme le Ge polycristallin est généralement de type P, il était nécessaire de convertir la couche de Ge polycristallin en type N, tout en conservant la qualité. Pour ce faire, après le premier traitement thermique par la méthode FLA, des impuretés de type N (phosphore) ont été implantées, et une seconde fois le FLA a été réalisé pour activer ces impuretés (Fig. 1). Cette méthode FLA en deux étapes a permis de produire un film de Ge polycristallin de type N de haute qualité.

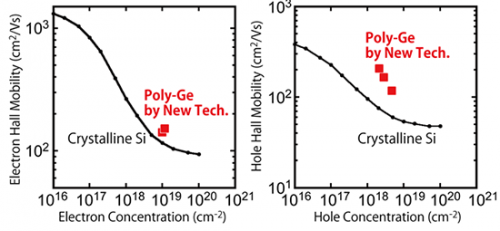

La mobilité à effet Hall représentant la qualité du film de Ge polycristallin produit par cette méthode est illustrée à la figure 2. Les films de Ge polycristallins de type N (électrons) et de type P (trous) avaient une mobilité qui dépassait celle du film de Ge monocristallin. Si. Cela montre qu'un transistor doté de propriétés supérieures au Si monocristallin pourrait être créé à l'aide d'un film de Ge polycristallin formé par la méthode développée.

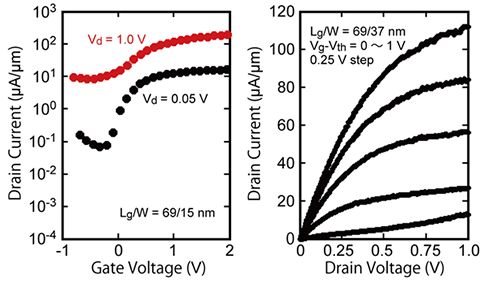

Un transistor Ge polycristallin de type N sans jonction (longueur de grille : 70 nm) a été produit en traitant le film de Ge polycristallin de type N décrit ci-dessus en une forme d'ailette et en formant en outre un alliage nickel-géranium (alliage Ni-Ge) dans le régions de source et de drain. Les caractéristiques de transfert et de sortie sont représentées sur la figure 3. La valeur du courant de drain à une tension de fonctionnement de 1 V approchait de près de 120 µA/µm, une valeur environ 10 fois supérieure à la valeur conventionnelle et équivalente à un MOSFET polycristallin de type Si N. de presque la même taille. On pense que la méthode FLA en deux étapes a amélioré le taux d’activation des impuretés par rapport à la valeur conventionnelle, diminuant ainsi la résistance parasitaire. La technologie développée a considérablement amélioré la vitesse de fonctionnement du transistor de type N, auparavant considéré comme le « goulot d'étranglement » du fonctionnement des circuits intégrés de transistors Ge polycristallins. Les transistors en Si polycristallin, qui ont tendance à être comparés aux transistors en Ge polycristallin, ont généralement des performances moins bonnes que les transistors en Si monocristallin. Les performances des transistors Ge polycristallins de type P dépassent déjà celles des transistors Si polycristallins et sont comparables à celles des transistors Si monocristallins. La méthode développée a ainsi fait de grands progrès vers la réalisation de circuits CMOS Ge polycristallins hautes performances.

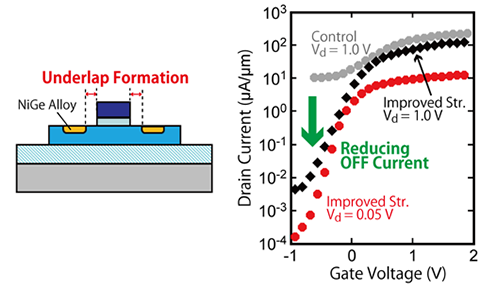

Dans les propriétés de transmission de la figure 3, le courant à l'état bloqué est important, de sorte que le rapport marche/arrêt lorsque 1 V était appliqué n'était que d'environ 10, ce qui posait problème. Par conséquent, afin de réduire le courant hors état, une structure prévoyant des espaces entre les électrodes Ni-Ge et la grille a été introduite, réduisant le courant hors état à 1/1000 (Fig. 4). Bien que le courant à l'état passant ait légèrement diminué, on peut s'attendre à un courant à l'état passant élevé et à un faible courant à l'état bloqué en optimisant les espaces entre les électrodes Ni-Ge et la grille.

Les projets futurs incluent la formation d'un circuit intégré combinant du Ge polycristallin de type P et de type N. transistor sur un film isolant et vérifier le fonctionnement du circuit. D'autres objectifs incluent le développement d'un 3D-LSI avec du Ge polycristallin empilé afin de miniaturiser considérablement le LSI, d'augmenter les performances et de réduire la consommation d'énergie.