การพัฒนาอุตสาหกรรม

ปรับปรุงคุณสมบัติทรานซิสเตอร์เจอร์เมเนียมโพลีคริสตัลไลน์อย่างมาก

ความร่วมมือด้านการวิจัยได้พัฒนาเทคโนโลยีการสร้างฟิล์มโพลีคริสตัลไลน์ใหม่เพื่อให้ได้เทคโนโลยีการซ้อนสามมิติ (3D) สำหรับวงจรรวมขนาดใหญ่ (LSI) ซึ่งช่วยปรับปรุงประสิทธิภาพของทรานซิสเตอร์โพลีคริสตัลไลน์เจอร์เมเนียม (Ge) ชนิด N อย่างมาก

Polycrystalline Ge สามารถเกิดขึ้นได้ที่อุณหภูมิต่ำกว่า (500 °C หรือต่ำกว่า) กว่าซิลิคอนโพลีคริสตัลไลน์ (Si) ที่ใช้กันอย่างแพร่หลาย ช่วยให้สามารถซ้อนวงจร CMOS ได้โดยตรง วงจรรวม โดยไม่ก่อให้เกิดความเสียหายจากความร้อน ซึ่งมีแนวโน้มว่าเป็นเทคโนโลยีองค์ประกอบสำหรับ 3D-LSI นอกจากนี้การเคลื่อนที่ของอิเล็กตรอนและรูใน Ge นั้นสูงกว่าใน Si ดังนั้นจึงคาดหวังการทำงานที่ความเร็วสูงและแรงดันไฟฟ้าต่ำ ต้องใช้ทรานซิสเตอร์ชนิด N และ P สำหรับการทำงานของวงจรรวม ทรานซิสเตอร์ชนิด P ของโพลีคริสตัลไลน์ Ge มีประสิทธิภาพเพียงพอแล้วซึ่งใกล้เคียงกับทรานซิสเตอร์ Si ผลึกเดี่ยวทั่วไป อย่างไรก็ตาม กระแสขับของทรานซิสเตอร์ชนิด N นั้นต่ำกว่ากระแสของทรานซิสเตอร์ Si ทั่วไปประมาณ 10 เท่าหรือมากกว่า ซึ่งเป็นปัญหา เทคโนโลยีที่พัฒนาขึ้นนี้เพิ่มกระแสการขับเคลื่อนประมาณ 10 เท่าเมื่อเทียบกับเทคโนโลยีทั่วไป ดังนั้นความเร็วในการทำงานของวงจรรวมโพลีคริสตัลไลน์ Ge จึงคาดว่าจะอยู่ในระดับที่จำเป็นสำหรับการใช้งานจริง และมีส่วนช่วยในการทำให้อุปกรณ์ 3D-LSI เกิดขึ้นจริง

รายละเอียดของเทคโนโลยีที่พัฒนาแล้วได้รับการประกาศใน “การประชุมอุปกรณ์อิเล็กตรอนนานาชาติประจำปี 2014” ที่จะจัดขึ้นที่ซานฟรานซิสโก ประเทศสหรัฐอเมริกา ระหว่างวันที่ 15-17 ธันวาคม 2014

ในปัจจุบัน ผู้คนจำนวนมากมีอุปกรณ์ไอที เช่น สมาร์ทโฟนและแท็บเล็ต และปริมาณข้อมูลที่ประมวลผลก็เพิ่มขึ้นอย่างมาก แม้ว่าจะต้องการปรับปรุงความสามารถในการประมวลผลข้อมูลของอุปกรณ์ IT ต่อไป แต่ปริมาณพลังงานที่ใช้ก็เพิ่มขึ้น ดังนั้นการให้อุปกรณ์ IT เหล่านี้ใช้พลังงานต่ำเป็นพิเศษจึงเป็นสิ่งสำคัญในการส่งเสริมสังคมที่ใช้พลังงานน้อยลง ในขณะที่ประสิทธิภาพสูงและการใช้พลังงานต่ำของ LSI สามารถทำได้ผ่านการย่อขนาดของทรานซิสเตอร์จนถึงขณะนี้ การย่อขนาดเพิ่มเติมได้พิสูจน์แล้วว่ามีความท้าทายทางเทคโนโลยีและเศรษฐกิจ ในขณะเดียวกัน วงจรรวม 3 มิติซึ่งมี LSI หลายตัวซ้อนกันไม่เพียงแต่ให้การบูรณาการสูงและประสิทธิภาพสูงโดยไม่ต้องใช้เทคโนโลยีย่อขนาด แต่ยังให้ประโยชน์ในการประหยัดพลังงานด้วยการลดความล่าช้าของสายไฟ วิธีการสร้างฟิล์มบางของ LSI ที่สร้างขึ้นแยกกันและซ้อนกันได้รับการพัฒนาขึ้นแต่มีค่าใช้จ่ายสูงและไม่ได้ปรับปรุงความหนาแน่นของสายไฟอย่างเพียงพอ ดังนั้นจึงเป็นที่พึงปรารถนาที่จะมีเทคโนโลยี 3D-LSI ใหม่ที่สร้างวงจร CMOS เพื่อซ้อนกันอย่างต่อเนื่องในชั้นการเดินสายของวงจรรวม CMOS และเชื่อมต่อกับสายไฟด้านบนและด้านล่าง

ร่วมกับ Tsutomu Tezuka (ผู้เชี่ยวชาญด้านการวิจัยแบบเข้มข้นเฉพาะ), Koji Usuda (ผู้เชี่ยวชาญด้านการวิจัยแบบเข้มข้นเฉพาะ) (ปัจจุบันอยู่กับ Toshiba Corporation ทั้งคู่) และคนอื่นๆ ของกลุ่มการพัฒนา CMOS วัสดุใหม่/โครงสร้างใหม่ ทีมวิจัยร่วม Green Nanoelectronics Center (GNC) ก่อตั้งขึ้นในสถาบันวิจัยนาโนอิเล็กทรอนิกส์ของ AIST ภายในสิ้นเดือนมีนาคม 2014 ได้ทำการวิจัยร่วมกันที่เกี่ยวข้องกับ MOSFET ชนิด P และ N โดยใช้ polycrystalline Ge (ข่าวประชาสัมพันธ์ของ AIST เมื่อวันที่ 12 ธันวาคม 2013) งานวิจัยนี้มีวัตถุประสงค์เพื่อพัฒนา LSI ที่มีประสิทธิภาพสูงกว่าและใช้พลังงานน้อยลง จากการวิจัยในปัจจุบัน ได้มีการแนะนำกระบวนการผลิตใหม่ๆ ซึ่งนำไปสู่การพัฒนาทรานซิสเตอร์โพลีคริสตัลไลน์ Ge ชนิด N ที่มีประสิทธิภาพสูงขึ้นไปอีก

การวิจัยนี้ดำเนินการ (ปีงบประมาณ 2010 ถึงปีงบประมาณ 2013) ที่ GNC โดยได้รับความช่วยเหลือจากโครงการระดมทุนสำหรับการวิจัยและพัฒนานวัตกรรมชั้นนำระดับโลกด้านวิทยาศาสตร์และเทคโนโลยีของสมาคมส่งเสริมวิทยาศาสตร์แห่งญี่ปุ่น ซึ่งเป็นระบบที่ออกแบบโดยสภานโยบายวิทยาศาสตร์และเทคโนโลยี

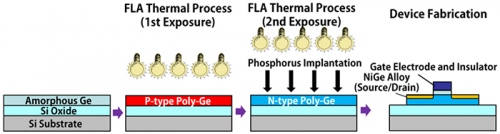

ฟิล์ม Polycrystalline Ge ที่ก่อตัวเป็นทรานซิสเตอร์จะเกิดขึ้นดังนี้: ชั้นออกไซด์ของความร้อน (SiO2) ถูกสร้างขึ้นบนพื้นผิว Si จากนั้นใช้วิธีการโปรยลงมาเพื่อสะสมฟิล์ม Ge ที่ไม่มีรูปร่าง จากนั้นจะถูกทำให้ตกผลึกโดยการประมวลผลด้วยความร้อนโดยใช้การหลอมด้วยหลอดไฟแฟลช ( เอฟแอลเอ) เมื่อใช้ฟิล์ม Polycrystalline Ge นี้เพื่อสร้างทรานซิสเตอร์ อุณหภูมิที่ใช้ในกระบวนการหลังการประมวลผลด้วยความร้อนจะอยู่ที่สูงสุด 350 °C โดยไม่ก่อให้เกิดความเสียหาย แม้ว่าจะมีวงจรรวมซึ่งรวมถึงสายทองแดงอยู่บนพื้นผิวก็ตาม ทรานซิสเตอร์ต้นแบบมีโครงสร้างทรานซิสเตอร์แบบไม่มีจุดต่อซึ่งมีรูปทรงครีบแสดงในแผนภาพในการสรุป (แผนภาพแนวคิดและแผนภาพโครงสร้าง) ช่องสัญญาณและชิ้นส่วนต้นทาง/ท่อระบายของทรานซิสเตอร์ชนิด N ที่ไม่มีจุดเชื่อมต่อต้องเป็นชนิด N ทั้งหมด อย่างไรก็ตาม เนื่องจากโพลีคริสตัลไลน์ Ge โดยปกติจะเป็นประเภท P จึงจำเป็นต้องแปลงชั้นโพลีคริสตัลไลน์ Ge เป็นประเภท N โดยที่ยังคงคุณภาพไว้ ในการทำเช่นนี้ หลังจากการประมวลผลความร้อนครั้งแรกโดยวิธี FLA จะมีการฝังสิ่งเจือปนชนิด N (ฟอสฟอรัส) ไว้ และดำเนินการ FLA เป็นครั้งที่สองเพื่อกระตุ้นสิ่งเจือปนเหล่านี้ (รูปที่ 1) วิธี FLA สองขั้นตอนนี้สามารถผลิตฟิล์ม Ge ชนิดโพลีคริสตัลไลน์ N คุณภาพสูงได้

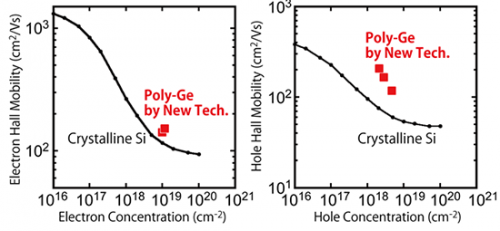

การเคลื่อนตัวของเอฟเฟกต์ฮอลล์ซึ่งแสดงถึงคุณภาพของฟิล์มโพลีคริสตัลไลน์ Ge ที่ผลิตโดยวิธีนี้แสดงในรูปที่ 2 ทั้งฟิล์มโพลีคริสตัลไลน์ Ge ทั้งชนิด N (อิเล็กตรอน) และชนิด P (รู) มีความคล่องตัวที่เหนือกว่าของผลึกเดี่ยว ศรี. นี่แสดงให้เห็นว่าทรานซิสเตอร์ที่มีคุณสมบัติเหนือกว่า Si ผลึกเดี่ยวสามารถสร้างขึ้นได้โดยใช้ฟิล์ม Ge แบบโพลีคริสตัลไลน์ที่เกิดจากวิธีการที่พัฒนาขึ้น

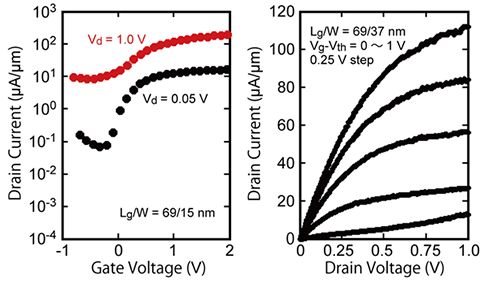

ทรานซิสเตอร์ Polycrystalline Ge ชนิด N แบบไม่มีรอยต่อ (ความยาวเกต: 70 นาโนเมตร) ถูกสร้างขึ้นโดยการประมวลผลฟิล์ม Ge ชนิดโพลีคริสตัลไลน์ N ที่อธิบายไว้ข้างต้นให้เป็นรูปทรงครีบและสร้างโลหะผสมนิกเกิล-เจอเรเนียมเพิ่มเติม (โลหะผสม Ni-Ge) ใน แหล่งที่มาและบริเวณท่อระบายน้ำ คุณลักษณะการถ่ายโอนและเอาต์พุตจะแสดงในรูปที่ 3 ค่ากระแสเดรนที่แรงดันไฟฟ้าขณะใช้งาน 1 V เข้าใกล้เกือบ 120 µA/µm ซึ่งเป็นค่าที่มากกว่าค่าทั่วไปประมาณ 10 เท่า และเทียบเท่ากับ MOSFET ชนิด Si N ชนิดโพลีคริสตัลไลน์ มีขนาดเกือบเท่ากัน เชื่อกันว่าวิธี FLA แบบสองขั้นตอนช่วยเพิ่มอัตราการกระตุ้นของสิ่งเจือปนได้มากกว่าค่าปกติ ส่งผลให้ความต้านทานต่อปรสิตลดลง เทคโนโลยีที่พัฒนาขึ้นได้ปรับปรุงความเร็วการทำงานของทรานซิสเตอร์ชนิด N อย่างเห็นได้ชัด ซึ่งก่อนหน้านี้ถือเป็น "คอขวด" ของการทำงานของวงจรรวมของทรานซิสเตอร์โพลีคริสตัลไลน์ Ge ทรานซิสเตอร์ Polycrystalline Si ซึ่งมีแนวโน้มที่จะเปรียบเทียบกับทรานซิสเตอร์ Polycrystalline Ge โดยทั่วไปแล้วจะมีประสิทธิภาพต่ำกว่าทรานซิสเตอร์ Single-crystalline Si ประสิทธิภาพของทรานซิสเตอร์ Polycrystalline Ge ชนิด P นั้นเหนือกว่าทรานซิสเตอร์ Polycrystalline Si แล้ว และทัดเทียมกับทรานซิสเตอร์ Single-crystalline Si วิธีการที่พัฒนาขึ้นทำให้เกิดความก้าวหน้าอย่างมากในการทำให้เกิดวงจร Polycrystalline Ge CMOS ประสิทธิภาพสูง

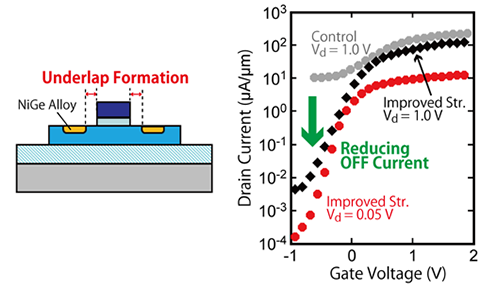

ในคุณสมบัติการส่งผ่านในรูปที่ 3 กระแสไฟฟ้านอกสถานะจะมีขนาดใหญ่ ดังนั้นอัตราส่วนการเปิด/ปิดเมื่อใช้ 1 V จึงอยู่ที่ประมาณ 10 เท่านั้น ซึ่งเป็นปัญหา ดังนั้น เพื่อลดกระแสนอกสถานะ จึงได้มีการแนะนำโครงสร้างที่ให้ช่องว่างระหว่างอิเล็กโทรด Ni-Ge และเกต เพื่อลดกระแสนอกสถานะลงเหลือ 1/1000 (รูปที่ 4) แม้ว่ากระแสในสถานะจะลดลงเล็กน้อย แต่กระแสในสถานะสูงและกระแสนอกสถานะต่ำสามารถคาดหวังได้โดยการปรับช่องว่างระหว่างอิเล็กโทรด Ni-Ge และเกต

แผนในอนาคตประกอบด้วยการสร้างวงจรรวมที่รวม Ge แบบโพลีคริสตัลไลน์ชนิด P และชนิด N ทรานซิสเตอร์ บนฟิล์มฉนวนและตรวจสอบการทำงานของวงจร เป้าหมายเพิ่มเติม ได้แก่ การพัฒนา 3D-LSI พร้อมด้วย Polycrystalline Ge แบบเรียงซ้อน เพื่อลด LSI ให้เล็กลงอย่างมาก เพิ่มประสิทธิภาพ และลดการใช้พลังงาน