PHÁT TRIỂN CÔNG NGHIỆP

Cải thiện đáng kể tính chất bóng bán dẫn germanium đa tinh thể

Một nhóm nghiên cứu hợp tác đã phát triển công nghệ tạo màng đa tinh thể mới để đạt được công nghệ xếp chồng ba chiều (3D) cho các mạch tích hợp (LSI) quy mô lớn, cải thiện đáng kể hiệu suất của bóng bán dẫn germanium đa tinh thể loại N (Ge).

Ge đa tinh thể có thể được hình thành ở nhiệt độ thấp hơn (500°C hoặc thấp hơn) so với silicon đa tinh thể (Si) được sử dụng rộng rãi. Điều này cho phép các mạch CMOS được xếp chồng trực tiếp lên mạch tích hợp mà không gây ra thiệt hại về nhiệt, đây hứa hẹn là một công nghệ cơ bản cho 3D-LSI. Ngoài ra, độ linh động của các electron và lỗ trống trong Ge cao hơn trong Si nên có thể hoạt động ở tốc độ cao và hoạt động ở điện áp thấp. Các bóng bán dẫn loại N và loại P được yêu cầu cho các hoạt động của mạch tích hợp. Các bóng bán dẫn loại P của Ge đa tinh thể đã đạt được hiệu suất đủ gần bằng các bóng bán dẫn Si đơn tinh thể thông thường. Tuy nhiên, dòng điện điều khiển của bóng bán dẫn loại N thấp hơn so với bóng bán dẫn Si thông thường từ 10 lần trở lên, đây là một vấn đề. Công nghệ được phát triển đã tăng dòng truyền động lên khoảng 10 lần so với công nghệ thông thường, do đó, tốc độ hoạt động của mạch tích hợp Ge đa tinh thể dự kiến sẽ ở mức cần thiết để sử dụng thực tế và góp phần hiện thực hóa các thiết bị 3D-LSI.

Các chi tiết về công nghệ được phát triển đã được công bố tại “Hội nghị Thiết bị Điện tử Quốc tế 2014” được tổ chức tại San Francisco, Hoa Kỳ vào ngày 15-17 tháng 12 năm 2014.

Ngày nay, nhiều người sở hữu các thiết bị CNTT như điện thoại thông minh và máy tính bảng và lượng thông tin được xử lý đã tăng lên đáng kể. Mặc dù mong muốn cải thiện hơn nữa khả năng xử lý thông tin của các thiết bị CNTT nhưng lượng điện năng mà chúng tiêu thụ ngày càng tăng, do đó việc cung cấp mức tiêu thụ điện năng cực thấp cho các thiết bị CNTT này là rất quan trọng trong việc thúc đẩy một xã hội tiêu thụ ít năng lượng hơn. Mặc dù cho đến nay, LSI hiệu suất cao và mức tiêu thụ điện năng thấp đã được thực hiện thông qua việc thu nhỏ bóng bán dẫn, nhưng việc thu nhỏ hơn nữa đã chứng tỏ là thách thức về mặt công nghệ và kinh tế. Trong khi đó, các mạch tích hợp 3D trong đó nhiều LSI được xếp chồng lên nhau không chỉ mang lại khả năng tích hợp cao và hiệu suất cao mà không cần công nghệ thu nhỏ mà còn mang lại lợi ích tiết kiệm năng lượng bằng cách giảm độ trễ của dây. Một phương pháp tạo màng mỏng các LSI được tạo riêng lẻ và xếp chồng chúng đã được phát triển nhưng tốn kém và không cải thiện đủ mật độ dây dẫn. Do đó, mong muốn có một công nghệ 3D-LSI mới có thể hình thành các mạch CMOS để xếp chúng liên tục trong một lớp nối dây của các mạch tích hợp CMOS và kết nối chúng với các dây trên và dưới.

Cùng với Tsutomu Tezuka (Chuyên gia nghiên cứu tập trung cụ thể), Koji Usuda (Chuyên gia nghiên cứu tập trung cụ thể) (cả hai đều hiện đang làm việc cho Tập đoàn Toshiba) và những người khác của Nhóm phát triển vật liệu mới/Cấu trúc mới CMOS, nhóm nghiên cứu hợp tác Trung tâm Điện tử nano xanh (GNC) được thành lập tại Viện nghiên cứu điện tử nano của AIST, vào cuối tháng 3 năm 2014, đã tiến hành nghiên cứu hợp tác liên quan đến MOSFET loại P và loại N sử dụng Ge đa tinh thể (Thông cáo báo chí của AIST vào ngày 12 tháng 12 năm 2013). Nghiên cứu này nhằm mục đích phát triển các LSI hiệu suất cao hơn, tiêu thụ ít năng lượng hơn. Thông qua nghiên cứu hiện tại, các quy trình sản xuất mới đã được giới thiệu, dẫn đến sự phát triển của bóng bán dẫn Ge đa tinh thể loại N với hiệu suất cao hơn nữa.

Nghiên cứu này được thực hiện (năm tài chính 2010 đến năm tài chính 2013) tại GNC với sự hỗ trợ từ Chương trình tài trợ cho R&D đổi mới hàng đầu thế giới về khoa học và công nghệ của Hiệp hội Xúc tiến Khoa học Nhật Bản, một hệ thống do Hội đồng Chính sách Khoa học và Công nghệ thiết kế.

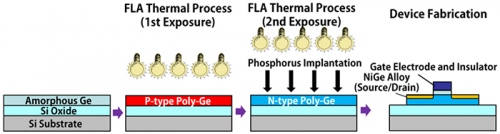

Một màng Ge đa tinh thể tạo thành các bóng bán dẫn được hình thành như sau: một lớp oxit nhiệt (SiO2) được hình thành trên đế Si, sau đó sử dụng phương pháp bắn tóe để lắng đọng một màng Ge vô định hình sau đó được kết tinh bằng quá trình xử lý nhiệt bằng cách ủ đèn flash ( FLA). Khi màng Ge đa tinh thể này được sử dụng để tạo thành bóng bán dẫn, nhiệt độ được sử dụng trong các quá trình sau xử lý nhiệt tối đa là 350°C, không gây hư hỏng, ngay cả khi tồn tại mạch tích hợp bao gồm cả dây đồng trên đế. Transitor nguyên mẫu có cấu trúc bóng bán dẫn không có mối nối với hình dạng vây được thể hiện trong các sơ đồ trong phần tóm tắt (sơ đồ khái niệm và sơ đồ cấu trúc). Tất cả các kênh và bộ phận nguồn/cống của bóng bán dẫn loại N không có mối nối đều phải thuộc loại N. Tuy nhiên, do Ge đa tinh thể thường là loại P nên cần phải chuyển đổi lớp Ge đa tinh thể thành loại N mà vẫn giữ được chất lượng. Để làm điều này, sau quá trình xử lý nhiệt đầu tiên bằng phương pháp FLA, tạp chất loại N (phốt pho) đã được cấy vào và FLA được thực hiện lần thứ hai để kích hoạt các tạp chất này (Hình 1). Phương pháp FLA hai bước này có thể tạo ra màng Ge đa tinh thể loại N chất lượng cao.

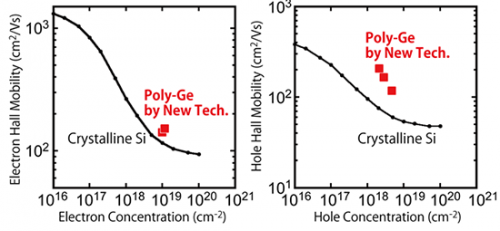

Độ linh động của hiệu ứng Hall thể hiện chất lượng của màng Ge đa tinh thể được tạo ra bằng phương pháp này được thể hiện trong Hình 2. Cả hai màng Ge đa tinh thể loại N (electron) và loại P (lỗ trống) đều có độ linh động vượt trội so với màng Ge đơn tinh thể Sĩ. Điều này cho thấy một bóng bán dẫn có đặc tính vượt trội so với Si đơn tinh thể có thể được tạo ra bằng cách sử dụng màng Ge đa tinh thể được hình thành bằng phương pháp đã phát triển.

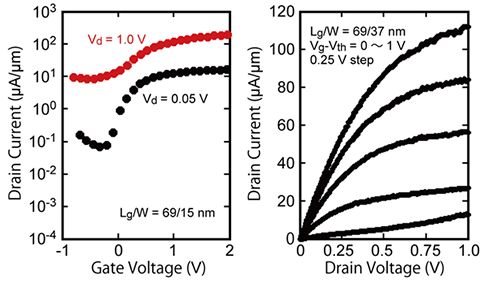

Một bóng bán dẫn Ge đa tinh thể loại N không có mối nối (chiều dài cổng: 70nm) được tạo ra bằng cách xử lý màng Ge đa tinh thể loại N được mô tả ở trên thành hình dạng vây và tạo thành thêm hợp kim niken-geranium (hợp kim Ni-Ge) trong vùng nguồn và vùng thoát nước. Các đặc tính truyền và đầu ra được thể hiện trong Hình 3. Giá trị dòng xả ở điện áp hoạt động 1 V đạt gần 120 µA/µm, giá trị lớn hơn khoảng 10 lần so với giá trị thông thường và tương đương với MOSFET loại Si N đa tinh thể có kích thước gần như nhau. Người ta tin rằng phương pháp FLA hai bước đã cải thiện tốc độ kích hoạt của tạp chất so với giá trị thông thường, làm giảm khả năng kháng ký sinh. Công nghệ được phát triển đã cải thiện rõ rệt tốc độ hoạt động của bóng bán dẫn loại N, trước đây được coi là “nút cổ chai” trong hoạt động mạch tích hợp của bóng bán dẫn Ge đa tinh thể. Các bóng bán dẫn Si đa tinh thể, thường được so sánh với các bóng bán dẫn Ge đa tinh thể, thường có hiệu suất kém hơn các bóng bán dẫn Si đơn tinh thể. Hiệu suất của bóng bán dẫn Ge đa tinh thể loại P đã vượt qua hiệu suất của bóng bán dẫn Si đa tinh thể và ngang bằng với bóng bán dẫn Si đơn tinh thể. Do đó, phương pháp được phát triển đã đạt được tiến bộ lớn trong việc hiện thực hóa các mạch Ge CMOS đa tinh thể hiệu suất cao.

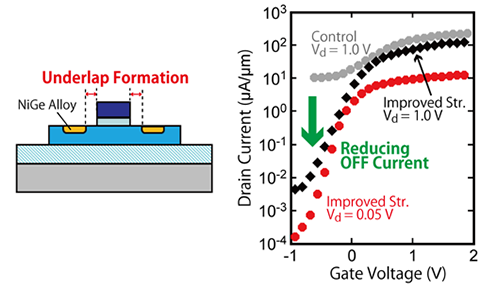

Trong đặc tính truyền dẫn ở Hình 3, dòng điện ở trạng thái tắt lớn, do đó tỷ lệ bật/tắt khi áp dụng 1 V chỉ khoảng 10, điều này có vấn đề. Do đó, để giảm dòng điện ngoài trạng thái, một cấu trúc cung cấp khoảng trống giữa các điện cực Ni-Ge và cổng đã được đưa vào, giảm dòng điện ngoài trạng thái xuống 1/1000 (Hình 4). Mặc dù dòng điện ở trạng thái bật giảm nhẹ, nhưng có thể dự đoán được dòng điện ở trạng thái bật cao và dòng điện ở trạng thái tắt thấp bằng cách tối ưu hóa khoảng cách giữa các điện cực Ni-Ge và cổng.

Các kế hoạch trong tương lai bao gồm việc hình thành một mạch tích hợp kết hợp Ge đa tinh thể loại P và loại N. Linh kiện bán dẫn lên một màng cách điện và kiểm tra hoạt động của mạch điện. Các mục tiêu xa hơn bao gồm phát triển 3D-LSI với Ge đa tinh thể xếp chồng lên nhau nhằm thu nhỏ đáng kể LSI, tăng hiệu suất và giảm mức tiêu thụ điện năng.