INDUSTRIEENTWICKLUNG

Erhebliche Verbesserung der Eigenschaften von polykristallinen Germaniumtransistoren

Eine Forschungskooperation hat eine neue polykristalline Filmbildungstechnologie entwickelt, um eine dreidimensionale (3D) Stapeltechnologie für hochintegrierte Schaltkreise (LSIs) zu erreichen und die Leistung von N-Typ-Transistoren aus polykristallinem Germanium (Ge) erheblich zu verbessern.

Polykristallines Ge kann bei einer niedrigeren Temperatur (500 °C oder weniger) gebildet werden als das weit verbreitete polykristalline Silizium (Si). Dadurch können CMOS-Schaltkreise direkt darauf gestapelt werden integrierte Schaltkreise ohne thermische Schäden zu verursachen, was als elementare Technologie für 3D-LSI vielversprechend ist. Darüber hinaus ist die Beweglichkeit von Elektronen und Löchern in Ge höher als in Si, sodass ein Hochgeschwindigkeitsbetrieb und ein Niederspannungsbetrieb zu erwarten sind. Für den Betrieb integrierter Schaltkreise sind N-Typ- und P-Typ-Transistoren erforderlich. P-Typ-Transistoren aus polykristallinem Ge haben bereits eine ausreichende Leistung erreicht, die der herkömmlicher einkristalliner Si-Transistoren nahe kommt. Allerdings ist der Treiberstrom von N-Typ-Transistoren um das Zehnfache oder mehr niedriger als der von herkömmlichen Si-Transistoren, was ein Problem darstellte. Die entwickelte Technologie erhöhte den Treiberstrom etwa um das Zehnfache gegenüber der herkömmlichen Technologie, so dass erwartet wird, dass die Betriebsgeschwindigkeit von integrierten Schaltkreisen aus polykristallinem Ge auf dem für den praktischen Einsatz erforderlichen Niveau liegt und zur Realisierung von 3D-LSI-Geräten beiträgt.

Die Einzelheiten der entwickelten Technologie wurden auf dem „2014 International Electron Device Meeting“ bekannt gegeben, das vom 15. bis 17. Dezember 2014 in San Francisco, USA, stattfindet.

Heutzutage verfügen viele Menschen über IT-Geräte wie Smartphones und Tablets und die Menge der verarbeiteten Informationen hat dramatisch zugenommen. Während eine weitere Verbesserung der Informationsverarbeitungsfähigkeit von IT-Geräten wünschenswert ist, nimmt der Stromverbrauch dieser IT-Geräte zu. Daher ist es wichtig, diesen IT-Geräten einen extrem niedrigen Stromverbrauch zu verleihen, um eine Gesellschaft zu fördern, die weniger Energie verbraucht. Während eine hohe Leistung und ein geringer Stromverbrauch von LSIs bisher durch Miniaturisierung von Transistoren erreicht wurden, hat sich eine weitere Miniaturisierung als technologische und wirtschaftliche Herausforderung erwiesen. Mittlerweile bieten integrierte 3D-Schaltkreise, in denen mehrere LSIs gestapelt sind, nicht nur eine hohe Integration und hohe Leistung ohne die Notwendigkeit einer Miniaturisierungstechnologie, sondern auch energiesparende Vorteile durch die Reduzierung der Leitungsverzögerung. Es wurde eine Möglichkeit entwickelt, dünne Filme aus individuell erstellten LSIs zu erzeugen und diese zu stapeln, ist jedoch kostspielig und verbessert die Verdrahtungsdichte nicht ausreichend. Daher ist es wünschenswert, über eine neuartige 3D-LSI-Technologie zu verfügen, die CMOS-Schaltkreise so bildet, dass sie kontinuierlich in einer Verdrahtungsschicht integrierter CMOS-Schaltkreise gestapelt und mit den oberen und unteren Drähten verbunden werden.

Zusammen mit Tsutomu Tezuka (Specified Concentrated Research Specialist), Koji Usuda (Specified Concentrated Research Specialist) (beide derzeit bei Toshiba Corporation) und anderen Mitgliedern der New Material/New Structure CMOS Development Group hat das gemeinsame Forschungsteam Green Nanoelectronics Center (GNC) Das im Nanoelektronik-Forschungsinstitut des AIST gegründete Unternehmen hatte bis Ende März 2014 gemeinsame Forschungen zu P-Typ- und N-Typ-MOSFETs unter Verwendung von polykristallinem Ge durchgeführt (AIST-Pressemitteilung vom 12. Dezember 2013). Ziel dieser Forschung war die Entwicklung leistungsstärkerer LSIs, die weniger Strom verbrauchen. Durch die vorliegende Forschung wurden neue Produktionsprozesse eingeführt, die zur Entwicklung polykristalliner Ge-Transistoren vom N-Typ mit noch höherer Leistung führten.

Diese Forschung wurde (GJ 2010 bis GJ 2013) am GNC mit Unterstützung des Förderprogramms für weltweit führende innovative Forschung und Entwicklung in Wissenschaft und Technologie der Japan Society for the Promotion of Science durchgeführt, einem System, das vom Rat für Wissenschafts- und Technologiepolitik entwickelt wurde.

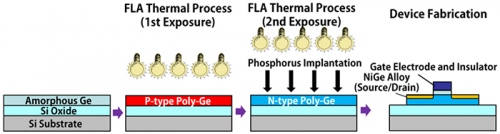

Ein polykristalliner Ge-Film, der Transistoren bildet, wird wie folgt gebildet: Eine thermische Oxidschicht (SiO2) wird auf einem Si-Substrat gebildet, dann wird das Sputterverfahren verwendet, um einen amorphen Ge-Film abzuscheiden, der dann durch thermische Verarbeitung unter Verwendung von Blitzlampenglühen kristallisiert wird ( FLA). Wenn dieser polykristalline Ge-Film zur Bildung eines Transistors verwendet wird, beträgt die Temperatur in den Prozessen nach der thermischen Verarbeitung maximal 350 °C, ohne dass es zu Schäden kommt, selbst wenn auf dem Substrat ein integrierter Schaltkreis mit Kupferdrähten vorhanden ist. Der Prototyp-Transistor hat eine verbindungslose Transistorstruktur mit der in den Diagrammen in der Zusammenfassung gezeigten Rippenform (konzeptionelles Diagramm und schematisches Diagramm der Struktur). Die Kanal- und Source/Drain-Teile eines übergangslosen N-Typ-Transistors müssen alle vom N-Typ sein. Da polykristallines Ge jedoch normalerweise vom P-Typ ist, war es notwendig, die polykristalline Ge-Schicht unter Beibehaltung der Qualität in den N-Typ umzuwandeln. Dazu wurden nach der ersten Wärmebehandlung mit der FLA-Methode N-Typ-Verunreinigungen (Phosphor) implantiert und ein zweites Mal eine FLA durchgeführt, um diese Verunreinigungen zu aktivieren (Abb. 1). Mit dieser zweistufigen FLA-Methode konnte ein hochwertiger polykristalliner Ge-Film vom N-Typ hergestellt werden.

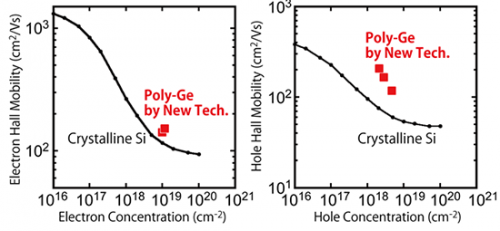

Die Hall-Effekt-Mobilität, die die Qualität des mit dieser Methode hergestellten polykristallinen Ge-Films darstellt, ist in Abb. 2 dargestellt. Sowohl die polykristallinen Ge-Filme vom N-Typ (Elektronen) als auch vom P-Typ (Löcher) hatten eine Mobilität, die die von einkristallinen übertraf Si. Dies zeigt, dass ein Transistor mit Eigenschaften, die denen von einkristallinem Si überlegen sind, mithilfe eines polykristallinen Ge-Films hergestellt werden konnte, der mit der entwickelten Methode gebildet wurde.

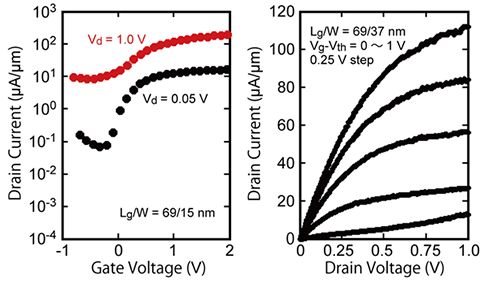

Ein übergangsloser polykristalliner Ge-Transistor vom N-Typ (Gatelänge: 70 nm) wurde hergestellt, indem der oben beschriebene polykristalline Ge-Film vom N-Typ in eine Flossenform verarbeitet und zusätzlich eine Nickel-Geranium-Legierung (Ni-Ge-Legierung) gebildet wurde Source- und Drain-Regionen. Die Übertragungs- und Ausgangseigenschaften sind in Abb. 3 dargestellt. Der Drain-Stromwert bei einer Betriebsspannung von 1 V näherte sich nahezu 120 µA/µm, ein Wert, der etwa zehnmal höher ist als der herkömmliche Wert und einem polykristallinen Si-N-MOSFET entspricht fast gleich groß. Es wird angenommen, dass die zweistufige FLA-Methode die Aktivierungsrate der Verunreinigungen gegenüber dem herkömmlichen Wert verbesserte und den parasitären Widerstand verringerte. Die entwickelte Technologie verbesserte die Betriebsgeschwindigkeit des N-Typ-Transistors deutlich, der zuvor als „Flaschenhals“ beim Betrieb integrierter Schaltkreise polykristalliner Ge-Transistoren galt. Polykristalline Si-Transistoren, die tendenziell mit polykristallinen Ge-Transistoren verglichen werden, weisen im Allgemeinen eine schlechtere Leistung auf als einkristalline Si-Transistoren. Die Leistung von polykristallinen Ge-Transistoren vom P-Typ übertrifft bereits die von polykristallinen Si-Transistoren und liegt auf dem Niveau von einkristallinen Si-Transistoren. Die entwickelte Methode machte somit große Fortschritte bei der Realisierung leistungsstarker polykristalliner Ge-CMOS-Schaltkreise.

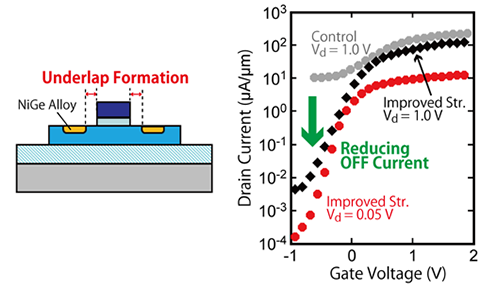

Bei den Übertragungseigenschaften in Abb. 3 ist der Sperrstrom groß, sodass das Ein-/Aus-Verhältnis beim Anlegen von 1 V nur etwa 10 betrug, was problematisch war. Um den Sperrstrom zu reduzieren, wurde daher eine Struktur eingeführt, die Räume zwischen den Ni-Ge-Elektroden und dem Gate bereitstellt, wodurch der Sperrstrom auf 1/1000 reduziert wird (Abb. 4). Während der Durchlassstrom leicht abnahm, kann durch die Optimierung der Abstände zwischen den Ni-Ge-Elektroden und dem Gate ein hoher Durchlassstrom und ein niedriger Ausschaltstrom erwartet werden.

Zukünftige Pläne umfassen die Bildung eines integrierten Schaltkreises, der polykristallines Ge vom P-Typ und N-Typ kombiniert Transistoren auf eine Isolierfolie aufgetragen und die Funktionsfähigkeit des Schaltkreises überprüft. Weitere Ziele umfassen die Entwicklung eines 3D-LSI mit gestapeltem polykristallinem Ge, um das LSI stark zu miniaturisieren, die Leistung zu steigern und den Stromverbrauch zu senken.